# TEST TIME REDUCTION BY SCAN CHAIN REORDERING

#### Pavel Bartoš

Doctoral Degree Programme (2), FIT BUT E-mail: xbarto41@stud.fit.vutbr.cz

Supervised by: Zdeněk Kotásek E-mail: kotasek@fit.vutbr.cz

**Abstract**: In this paper, methodology for scan chain optimisation performed after physical layout is presented. It is shown how the methodology can be used to decrease test time of component under test if scan chain is reorganized. The principles of the methodology are based on eliminating some types of faults in the physical layout and subsequent reduction of the number of test vectors needed to test the scan chain. As a result, component test application time is decreased. The methodology was verified on several circuits, experimental results are provided and discussed. It is expected that the results of our methodology can be used in mass production of electronic components where any reduction of test time is of great importance.

**Keywords**: scan chain, reorganization, reordering, physical layout, fault, diagnostics, test

### 1 INTRODUCTION

The increase of component density appearing in modern digital and analog devices requires new approaches to be used to test them, scan chain being one of these approaches. It holds that it was always very important to develop high quality tests used in the production phase. The identification of faulty components immediately after the production is certainly a cheaper procedure than their identification after it is included into an electronic device.

One possibility how to apply test to an electronic component is through its primary inputs/outputs. For complex components with high number of internal units, this approach cannot be used [1, 2]. The reason for scan-based approaches is to make internal components more controllable/observable during test application. Registers which cover certain function during operational mode are converted into serial shift registers through which test vectors / responses to them are transported. In our opinion, the reordering of scan chain to improve test quality needs to be studied. The reordering does not change the function of the component, it holds for testability parameters as well. In the past, the reordering of scan chain was used to simplify the process of routing [3] and to reduce power dissipation during test application through the reduction of switching activity [4]. Methods aiming at lowering static and dynamic power dissipation on the basis of test vectors or flip-flops reordering are known as well [5]. These methodologies have the increase of delay fault coverage as its goal as well [6].

When quality of test is evaluated, not only testability parameters but also the time needed to apply the test are important. It holds especially for tests used in the production phase of electronic component which are produced in high numbers. Even a short reduction of test application time has an impact on production costs. Faster/shorter tests can increase the number of components produced.

In our research, we deal with the idea of reducing the number of test vectors needed to verify proper function of circuit. As the input to the methodology, scan chain physical layout is used (the output of professional design system). Generally stated, we try to reduce the number of faults which can appear, thus reducing the number of test vectors to recognize these faults. It is clear that the number

of test vectors reduction results in test time decrease.

The structure of the paper is as follows. First, the motivation for our research is described. Then, the basic principles of the methodology are provided. Experimental results are presented and discussed together with our intentions for future research at the end of the paper.

### 2 MOTIVATION FOR THE RESEARCH

To manufacture a mixed-signal integrated circuits a lower resolution technology is still frequently used (typically  $0.25-0.7 \mu m$ ). It causes that complex circuits are spacious and manufacturing costs are high. One way how to cut manufacturing costs while maintaining chip area needed for the component implementation is through the reduction of interconnecting metal layers. This does not affect the analog part of the component significantly, because there are much less wires than in the digital part [7]. Anyway, in the digital part, the wires stretching and rising count of vias appear, because place and route tool can not realize the shortest path, and realizing of long wires is difficult, because the layers are overfilled. In some cases the place and route tool is unable to interconnect circuit parts and keep circuit area in predefined limits. Even when it is achieved, then a large number of long wires and metal vias results in lower component dependability.

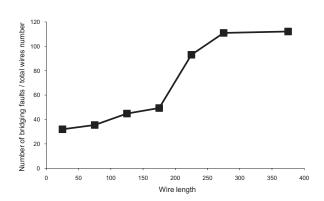

We compared wires length and possible bridging faults<sup>1</sup> list of a few real circuits which were gained from a company doing professional designs. We found that longer wires are more susceptible to create bridging faults then shorter wires, see graph of results in the figure 1. Long wires also have more vias between layers, so they are susceptible to openwire faults.

To test open-wire faults of metal vias, common test vectors for testing stuck-at faults can be used. But the testing of bridging faults requires higher number of test vectors because it is required to use each of 4 logic combinations to detect a bridging fault between a pair of wires.

**Figure 1:** Susceptibility to bridging faults dependence on wires length.

The goals of our research are based on the following hypotheses:

- 1. in the physical layout produced by a design system it is possible to identify long wires number of which can be reduced

- 2. as a consequence of the reduction, the number of test vectors to test bridging faults can be possibly decreased

- 3. based on the two hypotheses, we see the possibility of shortening testing phase after an electronic component is produced which can decrease production costs.

## 3 DESCRIPTION OF THE METHODOLOGY

During the design of a common integrated circuit, the length of wires cannot be affected. The only possibility exists during floorplanning by placing functional blocks in adjacent positions. The floorplanning is done by place and route tool, whose primary goal is to keep timing constraints. To summarize, we are not able to shorten connections between functional blocks.

<sup>&</sup>lt;sup>1</sup>a short-circuit between two signal lines [8]

However the interconnection of scan chain can be changed through the modification of flip-flops order. Scan chain is included to netlist after logic synthesis when the information on physical location of flip-flops is not available yet. Thus, the information about physical location of flip-flops cannot be used when the scan chain is included into the design. The inclusion is done on the level of logical structure.

In our research, we first tried to verify that after physical place and route procedure the circuit contains high number of long connections between flip-flops. For this purpose, a visualization tool was developed first which allowed us to recognize that many flip-flops are really interconnected by long connections which are routed through large chip area.

Based on the analysis of flip-flops locations, the interconnect of scan chain (order of flip-flops) can be changed in order to shorten lengths of wires. For the modified flip-flops order a re-route process is performed (without any change of flip-flops locations).

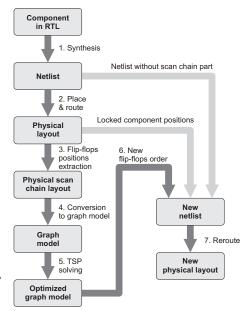

Then, the modified complete design process of an electronic component consists of the following steps (see Figure 2):

- 1. logic synthesis from register transfer level into netlist

- 2. physical place and route

- 3. modification of scan chain flip-flops order with flip-flops locations as the input

- 4. modification of netlist

- 5. new physical interconnection (re-route)

The goal of optimization is to minimize the length of interconnect wires between flip-flops.

The scan chain can be formalized into mathematical graph model, where the flip-flops are represented by nodes and the interconnecting wires by edges. The weights of edges are derived from the distances between flip-flops. It is evident that if a graph represents a scan chain it has to be a path.

Then the optimization problem can be transformed to traveling salesman problem which is very similar to our problem, except of the requirement to return back to the starting node. Traveling

**Figure 2:** Modified complete design process flow chart.

salesman problem is NP-hard problem [9]. To solve it, we can not use an exact algorithm because the best known exact algorithm has computational complexity in time of  $O(2^n)$  where n means number of nodes [10, 11] and scan chain may have thousands of flip-flops, the computational time would be unacceptable.

Therefore, it is necessary to use a heuristic or approximation algorithms. We chose an improved version of the Lin-Kernighan algorithm, the Concorde software package<sup>2</sup>[12] which incorporates the limited neighborhood structure as well as an additional optimizations. Concorde is widely regarded as the fastest TSP solver for large instances. It uses the chained Lin-Kernighan algorithm and search depth is greatly limited but high quality is obtained by repeatedly applying double-bridge transformations and optimization.

It was recognized that the Concorde algorithm eliminated problematical long wires and the total length of scan chains interconnections was reduced to 30-45% of original total length.

This improved reordered scan chain was included into original circuit and new reroute process was

<sup>&</sup>lt;sup>2</sup>freely available for academic research use

performed, results of which are described in the following section.

### 4 EXPERIMENTAL RESULTS

The method of optimization was verified on several real circuits which were gained from a company doing professional designs (see EXPER 01 – EXPER 04 in TABLE 1 - 2). The original parameters are available in TABLE 1.

| Table 1: | Test circu | iits narame | ters before | optimization. |

|----------|------------|-------------|-------------|---------------|

| Table 1. | TOST CHOU  | nto parame  | icis ocioic | obumization.  |

| Circuit                         | EXPER 01  | EXPER 02  | EXPER 03 | EXPER 04  |

|---------------------------------|-----------|-----------|----------|-----------|

| Number of gates                 | 41 821    | 28 565    | 16 136   | 45 880    |

| Number of scan chains           | 2         | 1         | 1        | 2         |

| Number of flip-flops            | 2 285     | 1 129     | 745      | 2 173     |

| Total number of bridging faults | 1 799 924 | 1 350 334 | 887 508  | 2 508 410 |

| (functional logic + scan chain) |           |           |          |           |

| Number of bridging faults       | 183 592   | 156 638   | 105 613  | 253 348   |

| in scan chain connections       |           |           |          |           |

| Total number of test vectors    | 820       | 459       | 1 134    | 2 175     |

| Test time                       | 46.92 ms  | 25.97 ms  | 42.28 ms | 118.27 ms |

These are the results which represent the solution after the physical layout was developed by a professional design system and set of test vectors generated.

The results gained by our optimization procedure are shown in TABLE 2.

Table 2: Result of optimizations.

| Table 2. Result of optimizations.        |           |           |          |           |  |  |  |  |

|------------------------------------------|-----------|-----------|----------|-----------|--|--|--|--|

| Circuit                                  | EXPER 01  | EXPER 02  | EXPER 03 | EXPER 04  |  |  |  |  |

| Total number of bridging faults          | 1 736 926 | 1 321 976 | 867 670  | 2 405 565 |  |  |  |  |

| (functional logic + scan chain)          |           |           |          |           |  |  |  |  |

| Number of bridging faults                | 115 762   | 106 758   | 66 932   | 158 849   |  |  |  |  |

| in scan chain connections                | 113 /02   |           |          |           |  |  |  |  |

| Total number of test vectors             | 764       | 439       | 1 102    | 2 005     |  |  |  |  |

| Test time                                | 43.72 ms  | 24.84 ms  | 41.09 ms | 109.03 ms |  |  |  |  |

| Ratio of total number of bridging faults | 96.5 %    | 97.9 %    | 97.8 %   | 95.9 %    |  |  |  |  |

| after/before optimization                |           |           |          |           |  |  |  |  |

| Ratio of bridging faults in scan chain   | 63.1 %    | 68.2 %    | 63.4 %   | 62.7 %    |  |  |  |  |

| connections after/before optimization    |           |           |          |           |  |  |  |  |

| Ratio of total number of test vectors    | 93.2 %    | 95.6%     | 97.2 %   | 92.2 %    |  |  |  |  |

| after/before optimization                | 93.2%     |           |          |           |  |  |  |  |

| Total test time reduction                | 3.2 ms    | 1.13 ms   | 1.19 ms  | 9.24 ms   |  |  |  |  |

The results prove that the hypotheses were correct and the method really allows to reduce the number of wires on which bridging faults can appear. In our experiments we took into account just the connections belonging to scan chain, the connections belonging to functional logic are excluded from the experiments. Then, after the reorganization was performed, the reduction of bridging faults was about 65 % of the value before the optimization. The reduction of bridging faults when all connections are considered (i. e. including the connections in functional logic) is about 96-98 % while the number of test vectors was reduced to 92-97 %. This difference is caused by unequal testability parameters of each component and its functional logic in terms of controllability / observability values.

The test application time reduction was evaluated for the situation when the shift of test vectors / responses to them through scan chain is synchronized with 20 MHz clock frequency.

### 5 CONCLUSIONS AND FUTURE RESEARCH

In this paper, the method which can reduce costs of testing by reducing the number of faults for which the circuit must be tested, is presented. This method is based on scan chain reordering to reduce length of connections between flip-flops. For our purposes, a software tool was developed which allows to visualize results of physical scan chain flip-flop placing. To reorder scan chain we used the methodology known as traveling salesman problem and for solving this problem we used the Concorde software package. The described method was tested on several real circuits and the test results confirmed that the approach really reduces the number of bridging faults which can appear in the structure. The reduction of test vectors amount and reduction of test time was confirmed as well.

The reduction of 3 - 8% may seem as not very significant, but this relatively small improvement is useful in mass production because it reduces testing cost and time needed to apply the test.

We also found out from results that the method has probably better results for larger circuits with more scan chains, but we need more test circuits to prove it.

In our future research we shall concentrate on the analysis of circuit physical layout and checking whether real wire length after place and route process is proportional to distance between flip-flops we used in the algorithm (Manhattan metric). To improve the results we shall modify this metric so that it penalizes routes which are short but in route way there are many other wires which cause many other vias to appear between layers in the final layout which are predisposed to open-wire faults.

#### **ACKNOWLEDGEMENTS**

The research was supported by the Grant Agency of the Czech Republic (GACR) No. 102/09/1668 – "SoC circuits reliability and availability improvement", by GACR No. GD102/09/H042 – "Mathematical and Engineering Approaches to Developing Reliable and Secure Concurrent and Distributed Computer Systems", by Research Project No. MSM 0021630528 – "Security-Oriented Research in Information Technology" and the grant "BUT FIT-S-10-1". During the research we cooperated very closely with ON Design Czech s.r.o. (ON Semiconductor design centrum).

# REFERENCES

- [1] M. T. Schmitz, B. M. Al-Hashimi, and P. Eles, System-Level Design Techniques for Energy-Efficient Embedded Systems. Norwell, MA, USA: Kluwer Academic Publishers, 2004.

- [2] M. Abadir and M. Breuer, "A knowledge-based system for designing testable vlsi chips," *IEEE Des. Test*, vol. 2, no. 4, pp. 56–68, 1985.

- [3] S. Makar, "A layout-based approach for ordering scan chain flip-flops," in *International Test Conference 1998 Proceedings*, USA, 1998, pp. 341–347.

- [4] S. Chakravarty and V. Dabholkar, "Minimizing power dissipation in scan circuits during test application," in *IEEE International Workshop on Low Power Design*, 1994, pp. 51–56.

- [5] J. Skarvada, "Digital Systems Test Application Optimization for Low Power Consumption," Ph.D. dissertation, Brno University of Technology, 2009.

- [6] W. Li, S. Wang, S. T. Chakradhar, and S. M. Reddy, "Distance restricted scan chain reordering to enhance delay fault coverage," in *VLSID '05: Proceedings of the 18th International Conference on VLSI Design held jointly with 4th International Conference on Embedded Systems Design.* USA: IEEE Computer Society, 2005, pp. 471–478.

- [7] R. A. Rutenbar and J. M. Cohn, "Layout tools for analog ics and mixed-signal socs: a survey," in *ISPD '00: Proceedings of the 2000 international symposium on Physical design.* USA: ACM, 2000, pp. 76–83.

- [8] E. Larsson, Introduction to Advanced System-on-Chip Test Design and Optimization. Springer, 2005.

- [9] D. L. Applegate, R. E. Bixby, V. Chvatal, and W. J. Cook, *The Traveling Salesman Problem: A Computational Study (Princeton Series in Applied Mathematics)*. Princeton University Press, 2007.

- [10] S. Kohn, A. Gottlieb, and M. Kohn, "A generating function approach to the traveling salesman problem," in *ACM '77: Proceedings of the 1977 annual conference.* USA: ACM, 1977, pp. 294–300.

- [11] R. M. Karp, "Dynamic programming meets the principle of inclusion and exclusion," *Operations Research Letters*, vol. 1, no. 2, pp. 49 51, 1982.

- [12] D. Applegate, R. Bixby, V. Chvatal, and W. Cook, "Concorde a code for solving traveling salesman problem." [Online]. Available: http://www.tsp.gatech.edu/concorde.html